# **PROSAK IC – PROgrammable Stand Alone Knock**

#### User's Guide

#### 1. Engine Knock Signal Processing

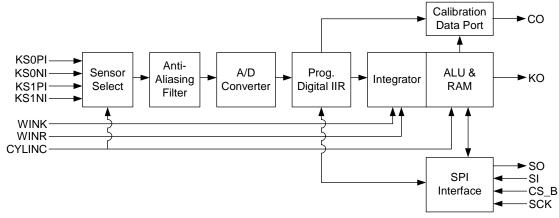

The PROSAK IC features a knock detection system that can interface with two knock sensors. The knock circuit uses an A/D converter, a fully programmable digital IIR filter, and knock signal detection processing. The IIR filters can be programmed per application requirements, or the knock system can be tailored using the calibration data port. The IC is designed to function for engines from three cylinders to twelve cylinders.

The knock sensor input is processed during a gating window function (WINK, WINR) generated externally via a microprocessor or custom circuitry. The PROSAK IC can be run in a single-window per cylinder mode (knock window only) or a dual-window per cylinder mode (knock window only). The knock sensor signals are filtered and integrated during the window events, and the output of the integrators can then be read directly through the SPI interface for software evaluation. The PROSAK IC also includes on-chip processing of the knock sensor signals and is capable of determining a knock condition via thresholding of knock signal intensity. The IC triggers a digital output pin (KO) when knock is indicated.

#### 1.1 Features:

- Two Sensor Inputs

- Fully programmable 8<sup>th</sup> order digital IIR filter

- On-chip integration of knock signal and reference signal

- Knock detection using knock vs. reference comparison plus threshold

- Knock Output pin to signal outside circuits of knock detection results

- External clock inputs of 20, 24, 28, 32, 36, and 40 MHz

- SPI interface

- Operating Temperature Range of -40°C to + 125°C

- Operating Voltage of  $5 \pm 0.25$  V

Figure 1.1 – Block Diagram of Prosak Knock System

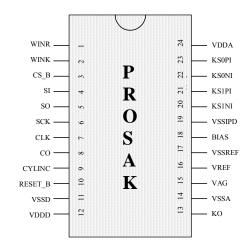

Figure 1.2 – Prosak IC, Top View

| Pin # | Pin Name | Description                                                                   |

|-------|----------|-------------------------------------------------------------------------------|

| 1     | WINR     | Reference Window – input for the reference integration window.                |

| 2     | WINK     | Knock Window – input for the knock integration window.                        |

| 3     | CS_B     | SPI Chip Select Bar. (active low)                                             |

| 4     | SI       | SPI Serial data In.                                                           |

| 5     | SO       | SPI Serial data Out.                                                          |

| 6     | SCK      | SPI Serial ClocK input.                                                       |

| 7     | CLK      | Clock. Main clock input for the chip                                          |

| 8     | СО       | Calibration Output. Used when calibrating knock                               |

| 9     | CYLINC   | Cylinder Increment. Increments the cylinder sequence counter.                 |

| 10    | RESET_B  | RESET. This pin should be tied to system reset.                               |

| 11    | VSSD     | Digital VSS. Digital negative supply pin.                                     |

| 12    | VDDD     | Digital VDD. Digital positive supply pin.                                     |

| 13    | KO       | Knock Output. Digital output to indicate knock was detected, or indicates the |

| 15    | KO       | knock calculation and/or reference calculation is valid.                      |

| 14    | VSSA     | Analog VSS. Analog negative supply pin.                                       |

| 15    | VAG      | Analog Ground. Used internally for a bias point.                              |

| 16    | VREF     | Voltage Calibration. Reference input for the Knock A/D converter. Connect     |

|       | V KLI    | to a precision 2.5 V voltage reference.                                       |

| 17    | VSSREF   | Voltage Ground Reference. Connect to the ground of the 2.5 V voltage          |

|       |          | reference.                                                                    |

| 18    | BIAS     | Bias Current. Used to set the bias current inside the IC.                     |

| 19    | VSSIPD   | Input protection VSS. Negative supply for input protection networks.          |

| 20    | KS1NI    | Knock Sensor 1 Negative Input.                                                |

| 21    | KS1PI    | Knock Sensor 1 Positive Input.                                                |

| 22    | KS0NI    | Knock Sensor 0 Negative Input.                                                |

| 23    | KSOPI    | Knock Sensor 0 Positive Input.                                                |

| 24    | VDDA     | Analog VDD. Analog positive supply pin.                                       |

Table 1.1 – Pin Descriptions

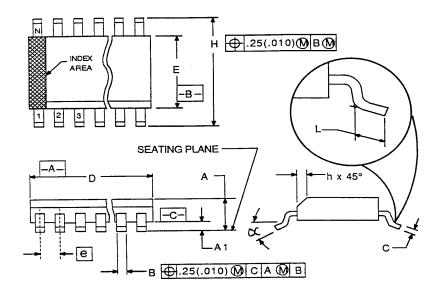

Figure 1.3 – Package Dimensions

| Dim. | Milli | meters | Inc   | ches   |

|------|-------|--------|-------|--------|

|      | Min.  | Max.   | Min.  | Max.   |

| А    | 2.35  | 2.65   | 0.093 | 0.104  |

| A1   | 0.10  | 0.25   | 0.004 | 0.009  |

| В    | 0.35  | 0.49   | 0.014 | 0.019  |

| С    | 0.25  | 0.32   | 0.010 | 0.012  |

| D    | 15.25 | 15.50  | 0.601 | 0.610  |

| E    | 7.40  | 7.60   | 0.292 | 0.299  |

| N    | 24    | -      | 24    |        |

| e    | 1.27  | BSC    | 0.0   | 50 BSC |

| Н    | 10.05 | 10.55  | 0.395 | 0.415  |

| h    | 0.25  | 0.75   | 0.010 | 0.029  |

| L    | 0.50  | 0.90   | 0.020 | 0.035  |

| α    | 0°    | 7°     | 0°    | 7°     |

Table 1.2 – Package Dimensions (related to Figure 1.3)

Notes: 1. Controlling Dimension: Millimeter

2. Dimension D and E do not include mold protrusion.

### Prosak IC

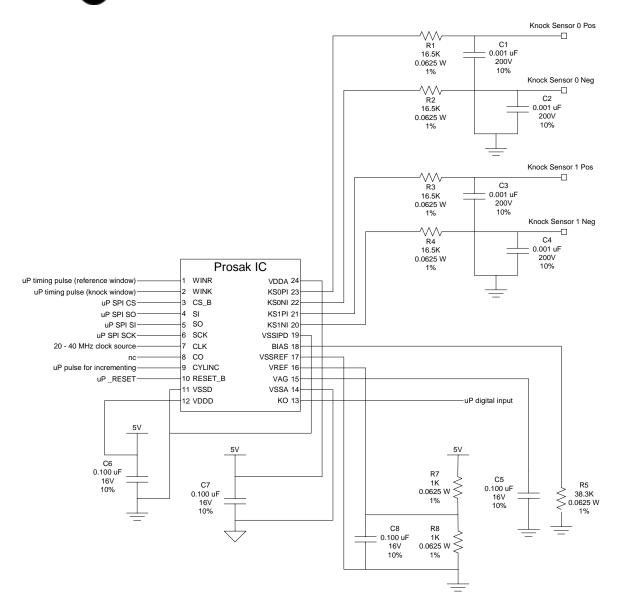

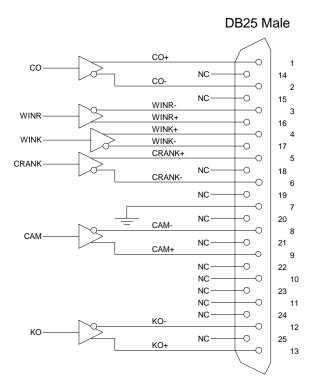

Figure 1.4 - Recommended Circuit Implementation\*

\* Notes:

intelligence

evervwhere

- 1. For a single window system, pin 1 (WINR) should be grounded.

- 2. The above circuit shows 2 knock sensors. For a system utilizing a single knock sensor, pins KS1PI and KS1NI can be no connects or can be grounded.

- 3. It is recommended that if possible, a precision 2.5V reference should be used in place of the circuit shown for VREF.

- 4. The CO pin is shown as a no connect. This pin is not used in normal operation, however it is used in the custom calibration tools for the IC. See Appendix A.

### 1.2 Maximum Ratings

| Characteristic                  | Symbol | Value         | Unit |

|---------------------------------|--------|---------------|------|

| DC Power Supply Voltage         | VDD    | -0.3, 7.00    | V    |

| Maximum Supply Current          | Idd    | 20            | mA   |

| Voltage from any pin to GND     | Vin    | -0.3, VDD+0.3 | V    |

| Storage Temperature Range       | Tstg   | -55, +150     | °C   |

| Junction Temperature            | Tj     | 150           | °C   |

| Lead Temp. during solder (10 s) | Ts     | 260           | °C   |

NOTE: Stress greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those listed in the following sections is NOT implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

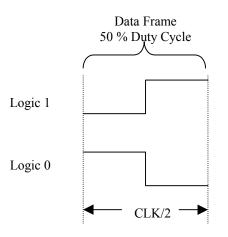

# 1.3 SPI, CLK, and CYLINC Circuit Performance

ELECTRICAL CHARACTERISTICS [VDD = 5.0V ± 5%, TA = -40 °C to 125 °C]

| Characteristic               | Symbol             | Min         | Тур | Max   | Unit |

|------------------------------|--------------------|-------------|-----|-------|------|

| SCK frequency                | f <sub>sck</sub>   |             |     | 8     | MHz  |

| SI setup time                | T <sub>SIS</sub>   | 30          |     |       | ns   |

| SI hold time                 | T <sub>SIH</sub>   | 10          |     |       | ns   |

| SCK to SO valid time         | T <sub>SOV</sub>   | 0           |     | 75    | ns   |

| SCK Pulse Width              | T <sub>CLKPW</sub> | 40          | 50  | 60    | %    |

| Delay after transfer: Normal | DT                 | $7/f_{CLK}$ |     |       | ns   |

| Operation                    |                    |             |     |       |      |

| Delay before SCK             | DSC                | 0           |     |       | ns   |

| CS_B, SCK, and SI Input      | V <sub>IH</sub>    | .7VDD       |     |       | V    |

| Voltage Threshold            | V <sub>IL</sub>    |             |     | .3VDD | V    |

| SO Output Drive              | V <sub>OH</sub>    | VDD-0.05    |     |       | V    |

|                              |                    | VDD - 0.4   |     |       | V    |

|                              | V <sub>OL</sub>    |             |     | 0.05  | V    |

|                              |                    |             |     | 0.4   | V    |

| CLK frequency                | f <sub>CLK</sub>   | 20          |     | 40    | MHz  |

| CLK                          | Vih                | .7VDD       |     |       | V    |

|                              | Vil                |             |     | .3VDD | V    |

| CYLINC Input                 | V <sub>IH</sub>    | .7VDD       |     |       | V    |

|                              | V <sub>IL</sub>    |             |     | .3VDD | V    |

Table 1.4 – SPI, CLK, and CYLINC Circuit Performance

# **1.4 Knock Circuit Performance**

The specifications below are for the complete KNOCK circuit measured at the I/O pads of the IC. To include external components simply include the attenuation caused by the external resistor network.

| ELECTRICAL CHARACTERISTICS [VDD = $5.0 \text{ V} \pm 5\%$ , TA = $-40 ^{\circ}\text{C}$ to $125 ^{\circ}\text{C}$ ] |  |

|---------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                     |  |

| Characteristic         | Symbol          | Condition                | Min   | Тур     | Max   | Unit |

|------------------------|-----------------|--------------------------|-------|---------|-------|------|

| Differential Input Imp | edance          | KSxPI to                 | 416   |         |       | kΩ   |

|                        |                 | KSxNI                    |       |         |       |      |

| Input Leakage          |                 |                          |       |         | 100   | nA   |

| Common Mode Reject     | tion            |                          | 40    |         |       | dB   |

| Common Mode Bias V     | Voltage         |                          |       | 2.77    |       | V    |

| Input sampling rate    |                 |                          |       | CLK /   |       | MHz  |

|                        |                 |                          |       | 128,    |       |      |

|                        |                 |                          |       | 192, or |       |      |

|                        |                 |                          |       | 256     |       |      |

| WINK and WINR          | V <sub>IH</sub> |                          | .7VDD |         |       | V    |

| Input                  | V <sub>IL</sub> |                          |       |         | .3VDD | V    |

| Window Length          |                 |                          |       |         | 87    | ms   |

| KO Output Drive        | V <sub>OH</sub> | $I_{LOAD} = 0 \ \mu A$   | VDD - |         |       | V    |

|                        |                 |                          | .05   |         |       |      |

|                        |                 | $I_{LOAD} = 250 \ \mu A$ | VDD - |         |       | V    |

|                        |                 |                          | 0.4   |         |       |      |

|                        | V <sub>OL</sub> | $I_{LOAD} = 0 \ \mu A$   |       |         | .05   | V    |

| Table 1.5 - Knock Circuit Performance |

|---------------------------------------|

|---------------------------------------|

### **1.5 Calibration Output Circuit Performance**

ELECTRICAL CHARACTERISTICS [VDD =  $5.0V \pm 5\%$ , TA = -40 °C to 125 °C]

| Characteristic  | Symbol          | Test Condition              | Min   | Тур | Max  | Unit |

|-----------------|-----------------|-----------------------------|-------|-----|------|------|

| CO Output Drive | V <sub>OH</sub> | $I_{LOAD} = 0 \ \mu A$      | VDD-  |     |      | V    |

|                 |                 |                             | 0.05  |     |      |      |

|                 |                 | $I_{LOAD} = 250 \ \mu A$    | VDD - |     |      | V    |

|                 |                 |                             | 0.4   |     |      |      |

|                 | V <sub>OL</sub> | $I_{LOAD} = 0 \ \mu A$      |       |     | 0.05 | V    |

|                 |                 | $I_{LOAD} = 2.5 \text{ mA}$ |       |     | 0.4  | V    |

| Table 1.6 - Calibration | Performance |

|-------------------------|-------------|

|-------------------------|-------------|

# 2. User Setup and Operation

The PROSAK IC processes data in the following manner (refer to Figure 1.1):

- 1. The sensor select block determines which knock sensor signal to pass through to the internal circuitry. The sensor is selected based on an on-chip cylinder counter.

- 2. The signal is passed through an anti-aliasing filter.

- 3. The output of the anti-aliasing filter is then over-sampled via a sigma-delta converter. The output of the converter is a 16-bit value which is updated at a rate determined by the internal clock frequency.

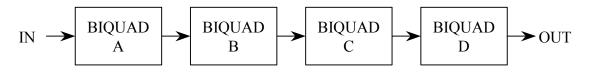

- 4. The sampled output is then passed through a programmable digital 8<sup>th</sup> order IIR filter (implemented as 4 cascading 2<sup>nd</sup> order filters).

- 5. During a knock window (WINK) or reference window (WINR), the absolute value of the output of the IIR filter is summed (integrated) and stored.

- 6. If desired, the PROSAK IC can be programmed for on-chip knock determination (binary condition of knock / no knock) with a digital output (KO) to signal an engine knock condition.

The values of the IIR filter coefficients are written to the PROSAK IC via the SPI interface. The values of the knock or reference signal integration can be read via the SPI interface for software calculation of knock if the user elects not to use the on-chip knock determination capabilities.

This section covers the software setup for each mode of operation of the PROSAK IC. Note that for each of the write registers described here, there is a corresponding read register to verify any information written to the IC if it is desirable for diagnostic purposes.

### 2.1.1 Single-Window Control

### 2.1.1.1 Initialization – Knock Determination via Software

The following steps must be taken to setup the IC via software at initialization.

- 1. Clock Setup: The internal clock must be set based on the external clock frequency supplied to the IC (see section 4). Address F1 (W-SETUP) must be set, but first the register must first be unlocked by sending information to address F0 (UNLOCK).

- 2. Cylinder Increment: The numbers of cylinders must be set via address F4 (W-CYLSETUP) (see section 5).

- 3. Sensor Select: The sensor numbers (0 or 1) corresponding to each cylinder number must be programmed at address E0 (W-KNKSS) (see section 6).

- 4. Filter Coefficients: The initial set of IIR filter coefficients must be programmed into the IC at addresses 80-93 (W-KNKCOEF) (see section 6).

- 5. Knock Setup: The setup for the knock system at address F7 (W-KNKSETUP1) must be set with the following actions (see section 6):

- a. Enable the IIR filter

- b. SSCHG set to 0. This changes the sensor select after knock calculation window, since there is no reference window.

- c. KOSEL should be set to 000.

- d. Set the other parameters in this register as needed for the application.

### 2.1.1.2 Initialization – Knock Determination On-Chip

In addition to be above initialization components, the following steps must be taken to setup the IC via software at initialization when on-chip knock processing. All registers are found in section 6 of this document. If the knock determination is made via software, these steps are not needed.

- 1. Thresholds: Set each cylinder threshold at addresses C0 CB (W-KNKTHR0-11).

- Reference Average: Write the reference averages to be used at addresses D0 (W-REFA0H), D1 (W-REFA0L), D2 (W-REFA1H), and D3 (W-REFA1L). These must be set since there is no updating of reference information automatically in single-window mode.

- 3. Knock Setup: The setup for the format of knock scale must be set at address F6 (W-KNKSETUP0).

- 4. Knock Setup: The setup for the knock system at address F7 (W-KNKSETUP1) must be set with the following actions (see section 6):

- a. Enable the IIR filter

- b. SSCHG set to 0. This changes the sensor select after knock calculation window, since there is no reference window.

- c. KOSEL must be set to 001.

- d. Set the other parameters in this register as needed for the application.

### 2.1.1.3 Synchronization

Upon synchronization of the engine, address F3 (W-CYLSYNC) must be set (see section 5).

### 2.1.1.4 Engine Operation

Depending on the application and calibration of an engine, it may be desirable to change the filter coefficients at different engine operating points. To do this, first disable the IIR filter by accessing address F7 (W-KNKSETUP1), update the IIR coefficients at addresses 80-93 (W-KNKCOEF), then re-enable the IIR filter by accessing address F7 (W-KNKSETUP1).

It may be desirable to check for overflows of the IIR filter periodically via address 78 (R-KKNKSTAT0).

If the knock determination is being made on-chip, then the thresholds at addresses C0 – CB (W-KNKTHR0-11) and the reference averages at addresses D0 (W-REFA0H), D1 (W-REFA0L), D2 (W-REFA1H), and D3 (W-REFA1L) may also be changed at any time.

# 2.1.2 Dual-Window Control

# 2.1.2.1 Initialization – Knock Determination via Software

The following steps must be taken to setup the IC via software at initialization.

- 1. Clock Setup: The internal clock must be set based on the external clock frequency supplied to the IC (see section 4). Address F1 (W-SETUP) must be set, but first the register must first be unlocked by sending information to address F0 (UNLOCK).

- 2. Cylinder Increment: The numbers of cylinders must be set via address F4 (W-CYLSETUP) (see section 5).

intelligence A everywhere

- 3. Sensor Select: The sensor numbers (0 or 1) corresponding to each cylinder number must be programmed at address E0 (W-KNKSS) (see section 6).

- 4. Filter Coefficients: The initial set of IIR filter coefficients must be programmed into the IC at addresses 80-93 (W-KNKCOEF) (see section 6).

- 5. Knock Setup: The setup for the knock system at address F7 (W-KNKSETUP1) must be set with the following actions (see section 6):

- a. Enable the IIR filter

- b. Set the SSCHG based on the desired window sequence

- c. KOSEL should be set to 000.

- d. Set the other parameters in this register as needed for the application.

# 2.1.2.2 Initialization – Knock Determination On-Chip

In addition to be above initialization components, the following steps must be taken to setup the IC via software at initialization when on-chip knock processing. All registers are found in section 6 of this document. If the knock determination is made via software, these steps are not needed.

- 1. Thresholds: Set each cylinder threshold at addresses C0 CB (W-KNKTHR0-11).

- 2. Reference Average Filtering: Set the filters used for the reference average at addresses CC (W-KNKCNU), CD (W-KNKCND), CE (W-KNKCKU), and CF (W-KNKCKD).

- 3. Knock Setup: The setup for the format of knock scale must be set at address F6 (W-KNKSETUP0).

- 4. Knock Setup: The setup for the knock system at address F7 (W-KNKSETUP1) must be set with the following actions (see section 6):

- a. Enable the IIR filter

- b. Set the SSCHG based on the desired window sequence

- c. KOSEL must be set to 001.

- d. Set the other parameters in this register as needed for the application.

# 2.1.2.3 Synchronization

Upon synchronization of the engine, address F3 (W-CYLSYNC) must be set (see section 5).

# 2.1.2.4 Engine Operation

Depending on the application and calibration of an engine, it may be desirable to change the filter coefficients at different engine operating points. To do this, first disable the IIR filter by accessing address F7 (W-KNKSETUP1), update the IIR coefficients at addresses 80-93 (W-KNKCOEF), then re-enable the IIR filter by accessing address F7 (W-KNKSETUP1).

It may be desirable to check for overflows of the IIR filter periodically via address 78 (R-KKNKSTAT0).

### 3. Serial Peripheral Interface

The SPI is the main communication system on the PROSAK IC. It allows the microcontroller unit (MCU) to communicate with the PROSAK IC as a 16 bit SPI slave device.

The MCU initiates a SPI transfer by asserting the slave select line connected to the CS\_B (Chip Select Bar) pin on the PROSAK IC. Data is simultaneously received (shifted in serially from the MCU on the SI pin) and transmitted (shifted out serially to the MCU on the SO pin). The data that is transmitted out on SO is in response to the command that was received on SI the previous time the MCU communicated with the PROSAK IC. A serial clock line (SCK) synchronizes shifting and sampling of information on the two serial data lines.

The SPI allows the MCU to read data out of all the registers located in the PROSAK IC. After receiving a request from SPI on the SI pin, the corresponding data is loaded to the shift register and transferred serially through the SO pin when the next transmission is made.

### 3.1 Implementation of the Serial Peripheral Interface

This section deals with the operation of the SPI, and command structure used by the SPI.

#### **3.1.1** Operation of the SPI

### 3.1.1.1 SPI: Single 8 Bit and Single 16 Bit Mode

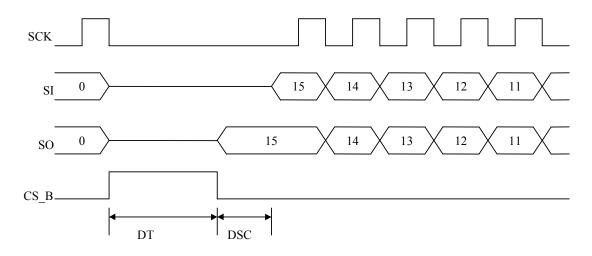

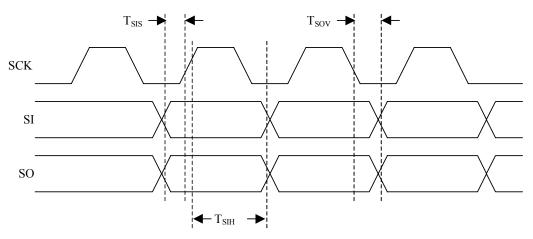

Figure 3.1 - SPI Transfer Timing Diagram

As shown in Figure 3.1, when the CS\_B pin is high, the SPI is idle and no communication is taking place over the SI and SO pins. The serial interface stays in the idle state until it detects that the PROSAK is being selected by the MCU (CS\_B is asserted). The MCU generates SCK, which the SPI uses to shift the data from the MCU into the SI pin and shifts the response to the previous command out the SO pin. After 16 SCKs, the PROSAK decodes the command that was received on the SI pin. The PROSAK then writes the data to the selected register (if the register is a write register) and always reads the data of the selected register to get ready for the next transfer.

intelligence A everywhere

In order to assure a successful SPI data transfer, certain timing restrictions must be observed by the MCU. These timing restrictions are listed in Table 1.4 and described here. As shown in Figure 3.1, once CS\_B is negated, it must remain high for a certain period of time known as DT (Delay after Transfer). Once CS\_B is asserted, there must be a delay specified by DSC (Delay until Serial Clock) before SCK begins.

### 3.1.1.2 SPI: Block Mode

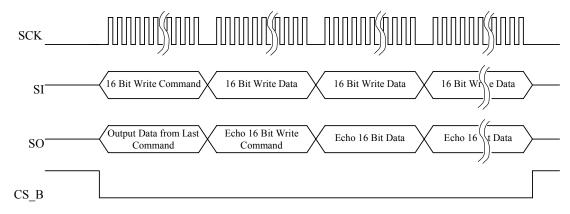

Figure 3.2 - SPI Transfer Block Write Timing Diagram

Figure 3.2 shows the SPI transfer timing diagram for a block write. During block write transfers, the PROSAK can be written with blocks of 16 bit data. The first 16 bits after CS\_B is asserted define the starting address to which the next 16 bit block of data received on SI will be written. The following 16 bit data blocks will be written in consecutive locations. After every 16 bit transfer, the data will be written on the data bus. The 16 bit frames will be interpreted as data until CS\_B is negated.

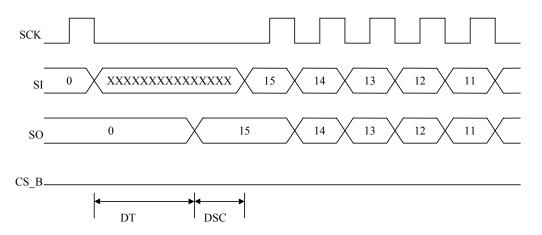

Figure 3.3 - SPI Transfer Block Write Timing Diagram with Timing Restrictions

In order to assure a successful SPI data transfer, certain timing restrictions must be observed by the MCU. These timing restrictions are listed in Table 1.4 and described here. As shown in Figure 3.3, DT refers to the time that elapses between the falling edge of the 16<sup>th</sup> SCK, and the

most significant bit of the output data being shifted out of SO. Once DT has elapsed, there must be a delay specified by DSC (Delay until Serial Clock) before SCK begins.

# 3.1.2 Serial Interface Command Structure

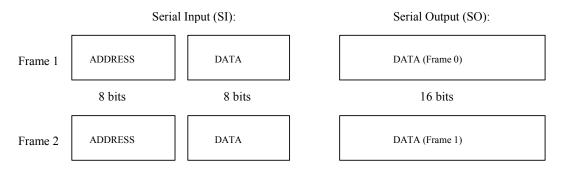

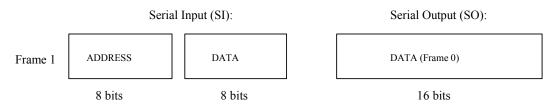

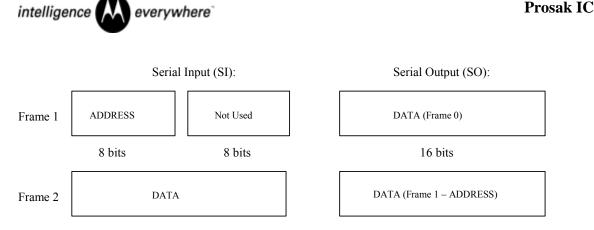

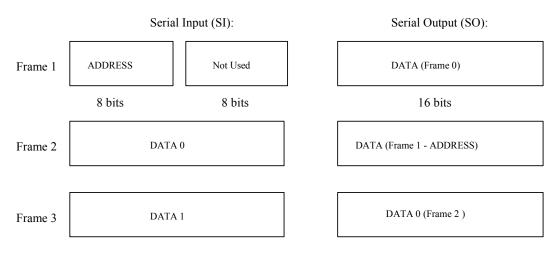

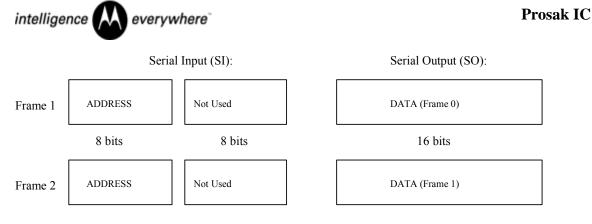

There are three types of write commands (single 8 bit data, single 16 bit data, and multiple 16 bit data) and one type of read command for the PROSAK IC. The write commands are used to modify registers in the PROSAK IC, for example setup registers or KNOCK programmable filter coefficients. The write commands automatically cause a read of the register being written, which is shifted out on SO in the next frame. The read command is use to read registers. All data transfers out of the SO pin are 16 bits.

# 3.1.2.1 SI-SO Relationship

The SPI shifts data in (SI) and out (SO) simultaneously. However, a response to a command is always delayed by one SPI transfer (i.e. response to the command N is shifted out at the same time command N+1 is shifted in).

Figure 3.4 - Example of SPI SI-SO relationship

# 3.1.2.2 Single 8 bit data write

A typical SPI write consists of one 16 bit frame. The frame transmitted by the CPU, into the SI pin, consists of 8 command bits and 8 data bits. The PROSAK returns 16 data bits on SO from the previously sent command. The CS\_B pin of the PROSAK IC must be asserted for all 16 bits. Note, the upper 16 locations are reserved for 8 bit register writes (F0H-FFH).

Figure 3.5 - Single 8-bit SPI Write Format

# 3.1.2.3 Single 16 bit data write

112 lower address locations (80H - EFH) are reserved for registers requiring more than 8 bits of data to be written to the PROSAK. These 112 addresses use the same address bits as the 8 bit data write, and the 16 data bits must follow in the next SPI transfer. The CS\_B pin must be asserted continuously for both frames. In this case the PROSAK echoes the command out of SO in the second frame while the 16 bit data is being shifted in on SI.

Figure 3.6 - Single 16 bit SPI Write Format

# 3.1.2.4 Block 16 bit data write

The 112 lower address locations (80H - EFH) access various sets of coefficients for the Knock functions. It may be convenient to write the continuous locations at once. This is accomplished by following the same procedure as the single 16 bit write, and continuing to send in the consecutive 16 bit data words while keeping CS\_B asserted. This alleviates the overhead of sending address and data for each location, by sending the starting address followed by multiple data. Negating CS\_B terminates multiple 16 bit writes. All of the 16 bit words up to the time CS\_B is negated will be written. If CS\_B is negated in the middle of a 16 bit word, the partially transmitted word will be ignored.

Figure 3.7 - Multiple 16 bit SPI Write Format

# 3.1.2.5 Read

A SPI read is used to read the registers in the PROSAK. The command transmitted by the CPU into the SI pin consists of 8 command bits and 8 don't care. The PROSAK returns 16 data bits on SO from the previously sent command. During the next frame transmitted by the CPU, the requested data from the PROSAK IC is shifted out of the SO pin. If no other data is immediately needed from the PROSAK, a NOP command may be sent in on SI to flush the requested data out of the SO pin. A NOP command is address 72 followed by 8 don't care bits to complete the 16-bit SPI message. The NOP will return zeros.

Figure 3.8 - SPI Read Format (any size data)

NOTE:

All timing is shown with respect to 30% VDD and 70% VDD.

Figure 3.9 - SI and SO Timing

# 4. Internal Clock Generator

In order to save a crystal oscillator, all the clocks on the PROSAK IC are derived from the CLK pin. A programmable divider divides the CLK pin to generate the internal clocks. The allowable CLK pin frequencies ( $f_{CLK}$ ) are 20, 24, 28, 32, 36, and 40 MHz. The internal clocks derived from the CLK pin are the knock modulator clocks.

The internal clock is generated by dividing the CLK pin by 128, 192, or 256. The divide-by ratio for the clock is controlled by the SETUP-0 register MODCLKF field. The modulator clock frequency must be configured per Table 4.1 for functionality of the Knock Circuit to be guaranteed.

| CLK            | MODCLKF    | Divide by | Internal Clock |

|----------------|------------|-----------|----------------|

| Frequency      | (values in | Ratio     | Frequency      |

| $f_{CLK}(MHz)$ | hex)       |           | (kHz)          |

| 40             | 0          | 256       | 156.3          |

| 36             | 1          | 192       | 187.5          |

| 32             | 1          | 192       | 166.7          |

| 28             | 1          | 192       | 145.8          |

| 24             | 2          | 128       | 187.5          |

| 20             | 2          | 128       | 156.3          |

Table 4.1 - Modulator Clock Divider Setup

### 4.1 Internal Clock Generator Registers

|                                                                                         | 0se two control bits define the divide by rate0 |

|-----------------------------------------------------------------------------------------|-------------------------------------------------|

|                                                                                         | e two control bits define the divide by rate 0  |

| that generates the in<br>00 – Divide by 256<br>01 – Divide by 192<br>10 – Divide by 128 | nternal clock from the CLK pin.                 |

This register is used to configure the core functions of the PROSAK IC.

| Address (F                                                                                                                                                                        | 0) W-UNLOCK – Write Unlock Register |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|

| Bit #                                                                                                                                                                             | Data to PROSAK                      | Reset |

| 15-8                                                                                                                                                                              | Address (F0)                        | 0     |

| 7-0                                                                                                                                                                               | Unlock Word = CA                    | 0     |

| This register is used to unlock the SETUP register. To modify the SETUP register, a write with the correct unlock word of CA must directly proceed a write to the SETUP register. |                                     |       |

| Bit #       | Data to PROSAK                                                                                                                                                                                            | Reset |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 15-8        | Address (F1)                                                                                                                                                                                              | 0     |

| 7-2         | Unused                                                                                                                                                                                                    | 0     |

| 1-0         | MODCLKF – These two control bits define the divide by rate<br>that generates the internal clock from the CLK pin.<br>00 – Divide by 256<br>01 – Divide by 192<br>10 – Divide by 128<br>11 – Divide by 192 | 0     |

| register, a | ster is used to configure the core functions of the PROSAK IC. To wr<br>a write to the UNLOCK register with the correct unlock data word must<br>he write to this register.                               |       |

# 5. Cylinder Increment

The cylinder circuit is a four bit counter that keeps track of the next cylinder that is to fire. The cylinder counter will count from zero to the number of cylinders-1. The counter will increment on every rising edge of the CYLINC signal. The counter can be synced to the correct cylinder by writing to the cylinder sync register.

The register CYLSETUP defines how many cylinders are configured, and the value to synchronize the counter to.

### 5.1 Implementation of the Cylinder Circuit

The counter will count from 0 to the value defined in MAXCYL. MAXCYL in the CYLSETUP register is the number of cylinders-1. The allowable number of cylinders is from 1 to 12. The counter will allow any number of cylinders from 1 to 16, but the knock circuit only supports from 1 to 12 cylinders.

The counter will be modified on every rising edge of CYLINC. If the value of the counter equals the value stored in MAXCYL, then on the next rising CYLINC edge, the counter will be loaded with 0, otherwise the counter will be loaded with the last counter value plus one.

The counter can be synchronized to the correct cylinder value by initializing the SYNCCYL field in the W-CYLSYNC register with the value to synchronize the counter to, and set the SSYNCCYL field in the W-CYLSYNC register to '1'. When the W-CYLSYNC register is written with the SSYNCCYL field bit set to '1', an internal flag will be set. This flag will indicate that on the next rising CYLINC edge, the value stored in the SYNCCYL field will be loaded into the counter, and the internal flag will be cleared.

# 5.2 Cylinder Registers

| Bit # | Data from PROSAK                                                                                                                                                                                 | Reset |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 15-4  | Unused                                                                                                                                                                                           | 0     |

| 3-0   | SYNCCYL – These 4 bits define the cylinder - 1 number that will<br>be loaded into the cylinder counter when the SSYNCCYL bit has<br>been written to a '1', and a rising CYLINC edge is detected. | 0     |

| Address (74   | ) R-CYLSETUP – Read Cylinder Setup Register                                                                                      |       |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|-------|

| Bit #         | Data from PROSAK                                                                                                                 | Reset |

| 15-8          | Unused                                                                                                                           | 0     |

| 7-4           | CYLVAL – These 4 bits define the current cylinder value.                                                                         | 0     |

| 3-0           | MAXCYL – These 4 bits define the number of cylinders – 1 that will be used. The Knock circuit supports only values from 0 to 11. | 0     |

| This register | r controls the setup and operation of the cylinder counter                                                                       | -     |

This register controls the setup and operation of the cylinder counter.

| 15-8       Address (F3)       0         7-5       Unused       0         4       SSYNCCYL – When this bit is written to '1', will set an internal flag that will indicate that during the next rising CYLINC edge, load the counter with the SYNCCYL field.       0         3-0       SYNCCYL – These 4 bits define the cylinder - 1 number that will       0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 SSYNCCYL – When this bit is written to '1', will set an internal flag that will indicate that during the next rising CYLINC edge, load the counter with the SYNCCYL field.                                                                                                                                                                                  |

| flag that will indicate that during the next rising CYLINC edge,<br>load the counter with the SYNCCYL field.                                                                                                                                                                                                                                                  |

| load the counter with the SYNCCYL field.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                               |

| 3-0 SYNCCVI - These 4 bits define the cylinder - 1 number that will (                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                               |

| be loaded into the cylinder counter when the SSYNCCYL bit has                                                                                                                                                                                                                                                                                                 |

| been written to a '1', and a rising CYLINC edge is detected.                                                                                                                                                                                                                                                                                                  |

| lı                                                                                                                                                                                                                                                                                                                                                            |

| Bit # | Data to PROSAK                                                                                           | Reset |

|-------|----------------------------------------------------------------------------------------------------------|-------|

| 15-8  | Address (F4)                                                                                             | 0     |

| 7-4   | Unused                                                                                                   | 0     |

| 3-0   | MAXCYL – These 4 bits define the number of cylinders that will be used. Values may be 0 to 11 inclusive. | 0     |

### 6. Knock Detection

This section defines the electrical and DSP implementation of the knock. The knock system consists of the following components (refer to Figures 1.1 and 1.4):

- 1. Knock sensor interface differential input pairs KS0PI/KS0NI and KS1PI/KS1NI

- 2. Sensor select

- 3. Anti-aliasing filter

- 4. A/D converter

- 5. Programmable IIR filter

- 6. Integrator

- 7. ALU & RAM

- 8. Knock output (KO)

### 6.1 Knock Sensor Interface

The broadband (or linear) sensor is modeled as a voltage source with a series capacitance and a resistance between the output connections. The recommended external RC network is shown in Figure 1.4.

### 6.2 Sensor Select

This stage allows selection of one of the two sensor inputs, either KS0PI/KS0NI or KS1PI/KS1NI, for each cylinder. The KNKSS register is used to select which knock sensor (either 0 or 1) will be used with each of twelve possible cylinders (from 0 to 11). The KNKSS register is used to read the status of the knock sensor select register.

For each cylinder, it is possible that the knock window be placed either before or after the reference window. In order for the Sensor Select to change sensors for the new cylinder, it must know the order of the knock and reference windows. SSCHG field in the KNKSETUP1 register accomplishes this by programming the sensor change to occur after either the knock window (0), or the reference window (1).

### 6.3 Anti-Aliasing Filter

The internal second order lowpass anti-aliasing filter is designed such that there is less than 1 dB of attenuation at frequencies below 25 kHz, and more than 50 dB of attenuation above the effective sampling rate.

# 6.4 A/D Converter

The A/D converter has unity gain by default. With unity gain, the converter can take inputs signals as large as  $\pm 2.5V$  (for VDD = 5.0V). If the input signals are within the range of  $\pm 1.25V$  (for VDD = 5.0V), the gain can be increased to two. This is done by setting KNKGAIN in the KNKSETUP1 register to a 1. (The default setting of KNKGAIN is 0, which results in unity gain on the converter).

### 6.5 Programmable IIR Filter

The digital programmable filter is a digital 8<sup>th</sup> order IIR filter. The programmable filter is implemented as a cascade of four digital biquads as shown in Figure 6.1. Each biquad can handle up to two poles and two zeros so that the entire filter can handle filter designs up to eight poles and eight zeros.

Figure 6.1 - System Flow Graph for Knock Digital IIR Filter

The filters have the form:

$$H(z) = \frac{b_{0A} + b_{1A}z^{-1} + b_{2A}z^{-2}}{1 + a_{1A}z^{-1} + a_{2A}z^{-2}} \times \frac{b_{0B} + b_{1B}z^{-1} + b_{2B}z^{-2}}{1 + a_{1B}z^{-1} + a_{2B}z^{-2}} \times \frac{b_{0C} + b_{1C}z^{-1} + b_{2C}z^{-2}}{1 + a_{1C}z^{-1} + a_{2C}z^{-2}} \times \frac{b_{0\underline{D}} + b_{1\underline{D}}z^{-1} + b_{2\underline{D}}z^{-2}}{1 + a_{1\underline{D}}z^{-1} + a_{2\underline{D}}z^{-2}}$$

Note:

$b_{0A}$  represents the  $b_0$  numerator coefficient for biquad A  $a_{2D}$  represents the  $a_2$  denominator coefficient for biquad D

Twenty total coefficients (five per biquad) are downloaded via SPI commands. Each coefficient is a 14-bit number limited to the range between -4.0 and +4.0. The coefficients must be downloaded to the PROSAK chip in sign-magnitude format into the KNKCOEFF registers. Reading the KNKCOEFF registers will output the last written filter coefficients.

The normal operation of the filter includes the following steps:

- 1. Program the filter coefficients.

- 2. Enable the filter with the IIRENABLE bit in the KNKSETUP1 register.

- 3. Wait for the transients of the step response to settle.

- 4. Begin an integration interval.

Whenever the user changes sensor inputs, the filter is reset. It is possible to change the filter response while in operation by clearing the IIRENABLE bit in the W-KNKSETUP1 register, and

then changing the filter coefficients. After the coefficients are altered, the IIRENABLE bit must be asserted and the filter will be reset.

### 6.6 Integrator

This stage performs two independent integrations of the filter output. The WINK and WINR windowing signals determine the duration of the integration. The integrators are 32 bit accumulators that are updated at the IIR filter rate (internal clock rate from Section 3). If the integrators overflow, the individual overflow flags will be set in the KNKSTATUS0 register.

### 6.7 Knock Detect

The Knock Detect circuit provides an output to indicate when knock has occurred. The knock detect block calculates the knock intensity and generates a knock output after the knock window and calculates the reference average after the reference window. A separate reference average is stored for each sensor.

### 6.7.1.1 Knock Cylinder Sampling

The Knock Detect supports one threshold per cylinder, and supports independent sensor select on a per cylinder basis. The Knock Detect block will sample the cylinder counter at the end of the knock window based on the value in the KNKSETUP register. The sampled value will be stored in the KNKCYL field of the KNKSTATUS1 register. The Knock Detect will use KNKCYL field to select the threshold register to use (KNKTHR0-11) during the knock intensity calculation. The KNKCYL field will also be used to index into the KNKSS register to pick the correct sensor.

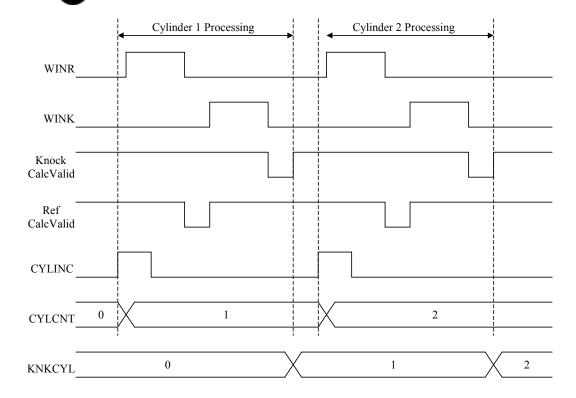

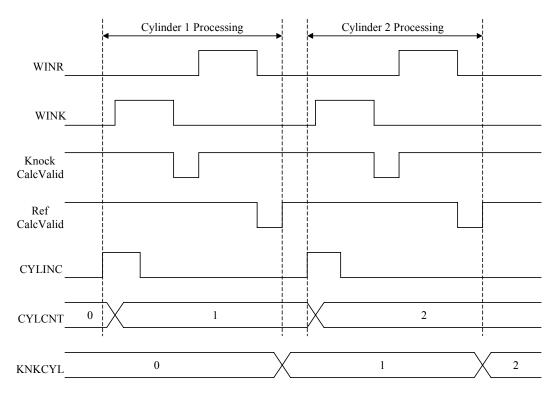

Figures 6.2 and 6.3 illustrates the knock cylinder counter system. The rising edge of CYLINC pin is the increment for the CYLCNT value, and will frame the current cylinder processing. The KNKCYL value is usually one cycle count behind the CYLCNT value as illustrated in the following figures. Note that the KNKCYL counter will be used to pick the threshold values, and the knock threshold values should account for this. In the examples below, during cylinder 2 processing, KNKTHR1 values will be accessed.

Figure 6.2 - KNKCYL Sequence Example With SSCHG=0

Figure 6.3 - KNKCYL Sequence Example With SSCHG=1

### 6.7.1.2 Reference Calculation

The background noise of the system is measured and integrated during the reference window and filtered in the Knock Detect block. The PROSAK supports two sensors, which requires two reference average values to be saved, one for each sensor.

After the falling edge of the reference window, the reference integration is presented to the Knock Detect block. The Knock Detect block will pass the reference integration value through a first order digital low pass filter to generate a new reference average. The filter calculates the reference average using the follow equation:

$REF_{avg_n} = C \times (REF_n - REF_{avg_{n-1}}) + REF_{avg_{n-1}}$

The  $\text{REF}_{\text{avgn}-1}$  is the last calculated reference average for the current sensor.  $\text{REF}_n$  is the reference integration valued measured during the reference window. C is a fractional filter coefficient, which is always less than 1. The reference values ( $\text{REF}_{\text{avg}}$ ) are stored in the REFA0H, REFA0L, REFA1H, and REFA1L registers.

In order to add flexibility and increase the performance of the filter's tracking capability, four coefficients can be used for the filter coefficient C. The coefficient C is programmable and is switched dynamically. If the filter is averaging up, one of two up averaging coefficients ( $C_{nu}$  and  $C_{ku}$ ) is used. If the filter is averaging down, one of two down averaging coefficients ( $C_{nd}$  and  $C_{kd}$ ) is used. Whether a knock occurred prior to the current reference integration determines which of the two up or down averaging coefficients is used. If knock occurred  $C_{nd}$  or  $C_{nu}$  is used. The up and down coefficients are used to help the filter track changes in the average reference level during such transient events. The knock coefficient can be used to slow the filter down to the extent that the current sample has hardly any effect on the average. The  $C_{nu}$ ,  $C_{ku}$ ,  $C_{nd}$ , and  $C_{kd}$  coefficients are stored in the KNKCNU, KNKCKU, KNKCKD and KNKCKD registers.

The Reference Calculation will be performed in the following order, and the bit lengths are described in Table 6.1:

$DELTA = (REF_n - REF_{avg_{n-1}})$  $NTEMP = (C \times DELTA)$  $REF_{avg_n} = (NTEMP + REF_{avg_{n-1}})$

| Name               | Description                                 | Bit Representation                      |

|--------------------|---------------------------------------------|-----------------------------------------|

| REF <sub>n</sub>   | 32 bit unsigned reference integration value | bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb  |

| DELTA              | 33 bit signed delta                         | sbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb  |

| С                  | 16 bit unsigned fractional coefficient      | 0.bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb |

| NTEMP              | 33 bit signed result                        | sbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb  |

| REF <sub>avg</sub> | 32 bit unsigned reference average           | bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb  |

Table 6.1 - Reference Calculation Bit Representation

### 6.7.1.3 Knock Calculation

The knock signal is measured and integrated during the WINK knock window. The knock ratio and intensity are calculated in the Knock Detect block. The PROSAK supports twelve threshold values, one for each cylinder to be used in the knock intensity calculation.

After the falling edge of the knock window, the knock integration value is sent to the Knock Detect block. The knock integration is used to calculate the knock intensity using the following equation:

Knock Intensity =  $\frac{\text{KNOCK}}{\text{REF}_{avg}}$  - Threshold

The threshold is selected based on cylinder to allow individual thresholds per cylinder. If the result of the knock intensity calculation is less than zero, the knock intensity is set to zero. The Ratio of KNOCK Integration value to the reference average is stored in the KNKR register. The Knock Intensity value is stored in the KNKI register. The thresholds are stored in the KNKTHR0-11 registers.

The Knock Calculation will be performed in the following order:

$$KNKR = \frac{KNOCK}{REF_{avg}}$$

$$KNKI = (KNKR - KNKTHR)$$

KNOCK is the 32 bit unsigned knock integration value, and  $\text{REF}_{avg}$  is the 32 bit unsigned reference average for the current cylinder. KNKR is the 16 bit unsigned ratio of the knock to reference. There is overflow logic to detect when the divider overflows. This output is visible through the calibration output and the KNKSTATUS1 register. If the KNKI operation generates a negative number, then the KNKI field is reported as zero.

The KNKSCALE field in the KNKSETUP0 register defines the format of KNKR, KNKI, and KNKTHR0-11. KNKSCALE determines where the decimal point is placed in these fields.

Depending on the ratio of the knock to reference window widths, the user may want to move the decimal point. For large ratios, it would be desirable to have the decimal point more to the right. For small ratios, it would be desirable to have the decimal point more to the left. By default, the decimal point is in the middle of the word. The KNKSCALE is set via address F6.

# 6.7.1.4 Knock/Reference Calculation Times

The KNOCKVAL flag in the KNKSTAT1 register defines when the KNKI and KNKR values are valid. During knock calculations, the KNOCKVAL flag will be cleared to indicate that new KNKI and KNKR values are being computed. The knock calculations begin after the falling edge of the knock window, and will complete after  $200/f_{CLK}$ .

The REFVAL flag in the KNKSTAT1 register defines when the reference average value is valid. During reference calculations, the REFVAL flag will be cleared to indicate that the new reference value is being computed. The reference calculations begin after the falling edge of the reference window, and will complete after  $260/f_{CLK}$ .

If the knock window falls while the reference calculations are computing, then the knock calculations will not start until the reference calculations are complete. If the reference window falls while the knock calculations are computing, then the reference calculations will not start until the knock calculations are complete. If both windows fall at the same time, the knock calculations will complete first, followed by the reference calculations.

# 6.7.1.5 KO Output Modes

The KO output pin can be programmed to indicate different Knock Detect Status. The KOSEL field in the KNKSETUP register defines what mode the KO pin will operate.

# 6.7.1.6 Knock Detect Status

The KNKSTATUS register gives the processor visibility into the Knock Detect block. The KNKCYL field in the KNKSTATUS register will report what cylinder is being processed by the Knock Detect block. The KIFLG field reports whether the KNKI is greater than zero. The KNOCKVAL field indicates that the KNKI and KNKR values are valid. The REFVAL field indicates that the REFAx values are valid. The status register also reports the IIR overflow flags the knock and reference integrator overflow flags, and the Knock Detect divide overflow flags. These overflow flags are set upon the error condition, and will hold their values until the processor reads the registers, then writes to the register with a zero in the overflow bit position to clear the flag.

| KOSEL    | Description                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (binary) | -                                                                                                                                                                                                                                |

| 000      | DISABLE - KO output pin disabled.                                                                                                                                                                                                |

| 001      | KIFLG – When the KNKI is greater than zero, the KO output will go high<br>and remain high until the next knock calculation. When the KNKI zero,<br>the KO output will go low and remain low until the next knock<br>calculation. |

| 010      | KNOCKVAL – The KO pin will be high when the knock results are valid,<br>and go low when the knock calculations are taking place and the KNKI<br>and KNKR values are invalid.                                                     |

| 011      | KIFLG or KNOCKVAL – This is the logical or of the KIFLG and KNOCKVAL fields.                                                                                                                                                     |

| 100      | REFVAL – The KO pin will be high when the reference results are valid,<br>and go low when the reference calculations are taking place and the<br>REFAx values are invalid.                                                       |

| 101      | KIFLG or REFVAL – This is the logical or of the KIFLG and REFVAL fields.                                                                                                                                                         |

| 110      | KNOCKVAL or REFVAL – This is the logical or of the KNOCKVAL and REFVAL fields.                                                                                                                                                   |

| 111      | Invalid.                                                                                                                                                                                                                         |

Table 6.2 - Knock KO Select Definition

# 6.8 Knock Registers

| Bit #   | Data from PROSAK                                                                        | Reset |

|---------|-----------------------------------------------------------------------------------------|-------|

| 15      | Coefficient Sign                                                                        |       |

| 14-13   | Coefficient Magnitude Integer (bit 14 is $2^1$ ; bit 13 is $2^0$ )                      |       |

| 12-2    | Coefficient Magnitude Fraction (bit 12 is 2 <sup>-1</sup> ; bit 2 is 2 <sup>-11</sup> ) |       |

| 1-0     | Reserved                                                                                |       |

|         |                                                                                         | ·     |

| Address | Data Field                                                                              | Reset |

| 00      | Coefficient a <sub>1,A</sub>                                                            | X     |

| 01      | Coefficient a <sub>1,B</sub>                                                            | X     |

| 02      | Coefficient a <sub>1,C</sub>                                                            | Х     |

| 03      | Coefficient a <sub>1,D</sub>                                                            | X     |

| 04      | Coefficient b <sub>0,A</sub>                                                            | X     |

| 05      | Coefficient b <sub>0,B</sub>                                                            | Х     |

| 06      | Coefficient b <sub>0,C</sub>                                                            | Х     |

| 07      | Coefficient b <sub>0,D</sub>                                                            | Х     |

| 08      | Coefficient b <sub>1,A</sub>                                                            | Х     |

| 09      | Coefficient b <sub>1,B</sub>                                                            | Х     |

| 0A      | Coefficient b <sub>1,C</sub>                                                            | Х     |

| 0B      | Coefficient b <sub>1,D</sub>                                                            | Х     |

| 0C      | Coefficient b <sub>2,A</sub>                                                            | Х     |

| 0D      | Coefficient b <sub>2,B</sub>                                                            | Х     |

| 0E      | Coefficient b <sub>2,C</sub>                                                            | Х     |

| 0F      | Coefficient b <sub>2,D</sub>                                                            | Х     |

| 10      | Coefficient a <sub>2,A</sub>                                                            | Х     |

| 11      | Coefficient a <sub>2,B</sub>                                                            | Х     |

| 12      | Coefficient a <sub>2,C</sub>                                                            | Х     |

| 13      | Coefficient $a_{2,D}$                                                                   | Х     |

These 20 registers are the IIR knock coefficient locations. The coefficient is a fourteen bit sign-magnitude number and has a range of -4.0 < coefficient < 4.0.

| Address (40 | –4B) R-KNKTHR0-11 – Read Knock Threshold Locations                      |         |

|-------------|-------------------------------------------------------------------------|---------|

| Bit #       | Data from PROSAK                                                        | Reset   |

| 15-0        | Threshold n                                                             | Х       |

| These 12 re | gisters contain the knock thresholds. The threshold is a sixteen bit po | ositive |

number. Address 40 contains the threshold for cylinder 0, and address 4B contains the threshold for cylinder 11.

| Address (4 | C) R-KNKCNU – Read Coefficient No Knock Up |       |

|------------|--------------------------------------------|-------|

| Bit #      | Data from PROSAK                           | Reset |

| 15-0       | C <sub>nu</sub> Coefficient No Knock Up    | Х     |

|            |                                            |       |

This register is the no knock up coefficient. The coefficient is a sixteen bit positive number and has a range of  $0 \le \text{coefficient} \le 1.0$ .

| Address (4 | D) R-KNKCND – Read Coefficient No Knock Down |       |

|------------|----------------------------------------------|-------|

| Bit #      | Data from PROSAK                             | Reset |

| 15-0       | C <sub>nd</sub> Coefficient No Knock Down    | Х     |

This register is the no knock down coefficient. The coefficient is a sixteen bit positive number and has a range of  $0 \le \text{coefficient} \le 1.0$ .

| Address (4E) R-KNKCKU – Read Coefficient Knock Up |                                      |       |

|---------------------------------------------------|--------------------------------------|-------|

| Bit #                                             | Data from PROSAK                     | Reset |

| 15-0                                              | C <sub>ku</sub> Coefficient Knock Up | Х     |

This register is the knock up coefficient location. The coefficient is a sixteen bit positive number and has a range of  $0 \le \text{coefficient} \le 1.0$ .

| Address (4F) R-KNKCKD – Read Coefficient Knock Down                                                                                                   |                                        |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|

| Bit #                                                                                                                                                 | Data from PROSAK                       | Reset |

| 15-0                                                                                                                                                  | C <sub>kd</sub> Coefficient Knock Down | Х     |

| This register is the knock down coefficient. The coefficient is a sixteen bit positive number and has a range of $0 \le \text{coefficient} \le 1.0$ . |                                        |       |

| Address (50) R-REFA0H – Read Reference Average 0 High |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Bit #                                                                                      | Data from PROSAK                      | Reset |  |

|--------------------------------------------------------------------------------------------|---------------------------------------|-------|--|

| 15-0                                                                                       | Reference Average 0 High (bits 31-16) | Х     |  |

| This is the upper 16 hits of the reference average 0 value. The average result is a 32 hit |                                       |       |  |

This is the upper 16 bits of the reference average 0 value. The average result is a 32 bit positive number.

| Address (51) R-REFA0L – Read Reference Average 0 Low |                                     |        |

|------------------------------------------------------|-------------------------------------|--------|

| Bit #                                                | Data from PROSAK                    | Reset  |

| 15-0                                                 | Reference Average 0 Low (bits 15-0) | Х      |

| T1 · · · · · 1                                       |                                     | 22.1.1 |

This is the lower 16 bits of the reference average 0 value. The average result is a 32 bit positive number.

| Address (52) R-REFA1H - Read Reference Average 1 High |                                       |       |

|-------------------------------------------------------|---------------------------------------|-------|

| Bit #                                                 | Data from PROSAK                      | Reset |

| 15-0                                                  | Reference Average 1 High (bits 31-16) | Х     |

|                                                       |                                       |       |

This is the upper 16 bits of the reference average 1 value. The average result is a 32 bit positive number.

| Address (53) R-REFA1L – Read Reference Average 1 Low                                                        |                                     |       |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|

| Bit #                                                                                                       | Data from PROSAK                    | Reset |

| 15-0                                                                                                        | Reference Average 1 Low (bits 15-0) | Х     |

| This is the lower 16 bits of the reference average 1 value. The average result is a 32 bit positive number. |                                     |       |

| Address (54) R-KNKR – Read Knock Ratio |                                  |       |

|----------------------------------------|----------------------------------|-------|

| Bit #                                  | Data from PROSAK                 | Reset |

| 15-0                                   | KNOCK / REF <sub>avg</sub> ratio | Х     |

|                                        |                                  |       |

This is the KNOCK / REFavg ratio register. The ratio is a sixteen bit positive number.

| Address (55) R-KNKI – Read Knock Intensity |                  |       |

|--------------------------------------------|------------------|-------|

| Bit #                                      | Data from PROSAK | Reset |

| 15-0                                       | Knock Intensity  | X     |

|                                            |                  |       |

This is the Knock Intensity register. The intensity is a sixteen bit positive number.

| Address (58) R-KNKIH – Read Knock Integrator High |                                    |       |

|---------------------------------------------------|------------------------------------|-------|

| Bit #                                             | Data from PROSAK                   | Reset |

| 15-0                                              | Knock Integrator High (bits 31-16) | Х     |

|                                                   |                                    |       |

This register is the upper 16 bits of the knock integrator value. The integrator result is a 32 bit positive number.

| Address (59) R-KNKIL – Read Knock Integrator Low |                                  |       |

|--------------------------------------------------|----------------------------------|-------|

| Bit #                                            | Data from PROSAK                 | Reset |

| 15-0                                             | Knock Integrator Low (bits 15-0) | X     |

|                                                  |                                  | 1     |

This register is the lower 16 bits of the knock integrator value. The integrator result is a 32 bit positive number.

| Address (5A) R-REFIH – Read Reference Integrator High |                                        |       |

|-------------------------------------------------------|----------------------------------------|-------|

| Bit #                                                 | Data from PROSAK                       | Reset |

| 15-0                                                  | Reference Integrator High (bits 31-16) | Х     |

This register is the upper 16 bits of the reference integrator value. The integrator result is a 32 bit positive number.

| Address (5B) R-REFIL – Read Reference Integrator Low                                           |                                      |       |

|------------------------------------------------------------------------------------------------|--------------------------------------|-------|

| Bit #                                                                                          | Data from PROSAK                     | Reset |

| 15-0                                                                                           | Reference Integrator Low (bits 15-0) | Х     |

| This register is the lower 16 bits of the reference integrator value. The integrator result is |                                      |       |

| Bit # | Data from PROSAK                                    | Reset |

|-------|-----------------------------------------------------|-------|

| 15-12 | Unused                                              | 0     |

| 11    | Cylinder 11, 0 – Knock Sensor 0, 1 – Knock Sensor 1 | 0     |

| 10    | Cylinder 10, 0 – Knock Sensor 0, 1 – Knock Sensor 1 | 0     |

| 9     | Cylinder 9, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 8     | Cylinder 8, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 7     | Cylinder 7, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 6     | Cylinder 6, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 5     | Cylinder 5, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 4     | Cylinder 4, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 3     | Cylinder 3, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 2     | Cylinder 2, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 1     | Cylinder 1, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| 0     | Cylinder 0, 0 – Knock Sensor 0, 1 – Knock Sensor 1  | 0     |

| Address (76                   | 5) R-KNKSETUP0 – Read Knock Setup Register                                                                                              |             |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Bit #                         | Data from PROSAK                                                                                                                        | Reset       |

| 15-6                          | Unused                                                                                                                                  | 0           |

| 5-0                           | KNKSCALE – Determines the position of the decimal point for<br>the KNKR0-11, KNKR, and KNKI<br>1F – bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb | 27          |

| This registe<br>are status bi | r is used to setup and monitor the knock block. Bits 5-0 are read-only ts.                                                              | y bits, and |

| Bit # | Data from PROSAK                                                 | Reset |

|-------|------------------------------------------------------------------|-------|

| 15-5  | Unused                                                           | 0     |

| 6     | SENALLUP – Sensor always update                                  | 0     |

|       | 0 - Sensor select to logic is only updated with the value in the |       |

|       | KNKSS register after the falling window, and the window's        |       |

|       | calculation is finished.                                         |       |

|       | 1 – Sensor select is always updated with the value in the KNKSS  |       |

|       | register.                                                        |       |

| 5     | IIRENBLE – Enable IIR filter.                                    | 0     |

|       | 0 – IIR Filter disabled, filter coefficients can be modified.    |       |

|       | 1 – IIR Filter enabled, filter coefficients locked               |       |

| 4     | KNKGAIN – A/D Gain.                                              | 0     |

|       | 0 - 1x                                                           |       |

|       | 1 – 2x                                                           |       |

| 3     | SSCHG – Sensor Select Change. Determines when to change the      | 0     |

|       | sensor select, and sample the cylinder counter.                  |       |

|       | 0 - After the knock calculations are complete                    |       |

|       | 1 – After the reference calculations are complete                |       |

| 2-0   | KOSEL – Selects the function of the KO pin                       | 0     |

|       | 000 - 0                                                          |       |

|       | 001 - Knock Indicator                                            |       |

|       | 010 - Knock Valid                                                |       |

|       | 100 - Reference Valid                                            |       |

|       | 110 - Knock Valid and Reference Valid                            |       |

| Address (78                                                                             | 3) R-KNKSTAT0 – Read Knock Status Register                            |           |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------|

| Bit #                                                                                   | Data from PROSAK                                                      | Reset     |

| 15-5                                                                                    | Unused                                                                | 0         |

| 4                                                                                       | Knock Detect Divider Overflow                                         | 0         |

| 3                                                                                       | Knock IIR Overflow Detection Biquad D.                                | 0         |

| 2                                                                                       | Knock IIR Overflow Detection Biquad C.                                | 0         |

| 1                                                                                       | Knock IIR Overflow Detection Biquad B.                                | 0         |

| 0                                                                                       | Knock IIR Overflow Detection Biquad A.                                | 0         |

| This registe                                                                            | r contains the status bits for knock including the knock IIR overflow | detection |

| bits. The Overflow bits can only be cleared by reading asserted, and writing a 0 in the |                                                                       |           |

| desired bit position.                                                                   |                                                                       |           |

| Bit # | Data from PROSAK                             | Reset |

|-------|----------------------------------------------|-------|

| 15-7  | Unused                                       | 0     |

| 6     | REFVAL – Reference Calculation Valid         | 0     |

|       | 0 – Reference average is not valid.          |       |

|       | 1 – Reference average is valid.              |       |

| 5     | KNOCKVAL – Knock Calculation Valid           | 0     |

|       | 0 – Knock Ratio and Intensity are not valid. |       |

|       | 1 – Knock Ratio and Intensity are valid.     |       |

| 4     | KIFLG – Knock Indicator                      | 0     |

|       | 0 - Knock not detected.                      |       |

|       | 1 – Knock detected.                          |       |

| 3-0   | KNKCYL – Knock Cylinder current value        | 0     |

| Bit #   | Data to PROSAK                                                                          | Reset |

|---------|-----------------------------------------------------------------------------------------|-------|